R8A77800ANBGAV Renesas Electronics America, R8A77800ANBGAV Datasheet - Page 38

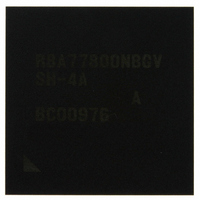

R8A77800ANBGAV

Manufacturer Part Number

R8A77800ANBGAV

Description

IC SUPERH MPU ROMLESS 449-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77800ANBGV.pdf

(1342 pages)

Specifications of R8A77800ANBGAV

Core Processor

SH-4A

Core Size

32-Bit

Speed

400MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

75

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

449-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77800ANBGAV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 38 of 1342

- Download datasheet (7Mb)

Figure 21.12 Sample Serial Reception Flowchart (2)................................................................. 780

Figure 21.13 Sample SCIF Receive Operation

(Example with 8-Bit Data, Parity, One Stop Bit) .................................................. 782

Figure 21.14 Sample Operation Using Modem Control (SCIF0_RTS) (Only in Channel 0)..... 782

Figure 21.15 Data Format in Clocked Synchronous Communication ........................................ 783

Figure 21.16 Sample SCIF Initialization Flowchart ................................................................... 785

Figure 21.17 Sample Serial Transmission Flowchart ................................................................. 786

Figure 21.18 Sample SCIF Transmission Operation in Clocked Synchronous Mode................ 787

Figure 21.19 Sample Serial Reception Flowchart (1)................................................................. 788

Figure 21.19 Sample Serial Reception Flowchart (2)................................................................. 789

Figure 21.20 Sample SCIF Reception Operation in Clocked Synchronous Mode ..................... 790

Figure 21.21 Sample Simultaneous Serial Transmission and Reception Flowchart................... 791

Figure 21.22 Receive Data Sampling Timing in Asynchronous Mode ...................................... 795

Figure 21.23 Example of Synchronization Clock Transfer by DMAC ...................................... 796

Section 22 Serial I/O with FIFO (SIOF)

Figure 22.1 Block Diagram of SIOF .......................................................................................... 798

Figure 22.2 Serial Clock Supply................................................................................................. 827

Figure 22.3 Serial Data Synchronization Timing ....................................................................... 829

Figure 22.4 SIOF Transmit/Receive Timing .............................................................................. 830

Figure 22.5 Transmit/Receive Data Bit Alignment .................................................................... 832

Figure 22.6 Control Data Bit Alignment .................................................................................... 833

Figure 22.7 Control Data Interface (Slot Position)..................................................................... 834

Figure 22.8 Control Data Interface (Secondary FS) ................................................................... 835

Figure 22.9 Example of Transmit Operation in Master Mode.................................................... 838

Figure 22.10 Example of Receive Operation in Master Mode ................................................... 839

Figure 22.11 Example of Transmit Operation in Slave Mode .................................................... 840

Figure 22.12 Example of Receive Operation in Slave Mode ..................................................... 841

Figure 22.13 Transmit and Receive Timing (8-Bit Monaural Data (1))..................................... 845

Figure 22.14 Transmit and Receive Timing (8-Bit Monaural Data (2))..................................... 845

Figure 22.15 Transmit and Receive Timing (16-Bit Monaural Data) ........................................ 846

Figure 22.16 Transmit and Receive Timing (16-Bit Stereo Data (1)) ........................................ 846

Figure 22.17 Transmit and Receive Timing (16-Bit Stereo Data (2)) ........................................ 847

Figure 22.18 Transmit and Receive Timing (16-Bit Stereo Data (3)) ........................................ 847

Figure 22.19 Transmit and Receive Timing (16-Bit Stereo Data (4)) ........................................ 848

Figure 22.20 Transmit and Receive Timing (16-Bit Stereo Data).............................................. 848

Section 23 Serial Protocol Interface (HSPI)

Figure 23.1 Block Diagram of HSPI .......................................................................................... 850

Figure 23.2 Operational Flowchart............................................................................................. 861

Figure 23.3 Timing Conditions when FBS = 0........................................................................... 863

Rev.1.00 Dec. 13, 2005 Page xxxvi of l

Related parts for R8A77800ANBGAV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: