R8A77800ANBGAV Renesas Electronics America, R8A77800ANBGAV Datasheet - Page 480

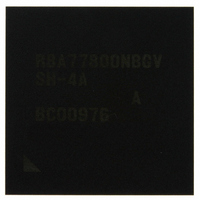

R8A77800ANBGAV

Manufacturer Part Number

R8A77800ANBGAV

Description

IC SUPERH MPU ROMLESS 449-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77800ANBGV.pdf

(1342 pages)

Specifications of R8A77800ANBGAV

Core Processor

SH-4A

Core Size

32-Bit

Speed

400MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

75

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

449-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77800ANBGAV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 480 of 1342

- Download datasheet (7Mb)

Section 12 DDR-SDRAM Interface (DDRIF)

3. The STR settings do not establish a relationship between the timing of the PREALL and REFA

4. Make the SDRAM enter the self-refresh state by setting the DRE and RMODE bits in MIM to

5. The DDRIF automatically issues the self-refresh command and sets the CKE pin low. The

6. Read the SELFS status bit in MIM to check whether or not the SDRAM has actually entered

[Return from self-refresh state]

1. Clear the RMODE and DRE bits in MIM to 0 to take the DDS-SDRAM out of the self-refresh

2. Read the SELFS status bit in MIM to check whether or not the SDRAM has actually returned

3. After allowing the time required for recovery from the self-refresh state, set registers so that

4. When access becomes possible, use the SMS bits in SCR to issue the REFA (auto-refresh)

5. Dummy read a byte from any SDRAM address.

6. Use the SMS bits in SCR to issue the PREALL (all-bank precharge) command.

7. Use the SMS bits in SCR to issue the REFA command. This operation is required to make the

8. Set MIM so that the counter for the auto-refresh function starts counting and thus drives auto-

(2)

Clearing or setting the PCKE bit in MIM changes the level of the CKE pin, the SDRAM enters or

leaves the power-down mode. The SDRAM in this mode consumes less power.

Since the SDRAM is made to enter the power-down mode after each round of memory access and

has to leave the power-down mode before each round of memory access, an overhead of one cycle

of the MCLK is incurred in each case.

Rev.1.00 Dec. 13, 2005 Page 428 of 1286

REJ09B0158-0100

commands that are issued by using SCR. A period of waiting that is suitable for the memory

unit must be inserted.

1 (in this case, the value of the DCE bit should be left at 1).

SDRAM then automatically enters the self-refresh mode.

the self-refresh mode.

state.

from the self-refresh mode.

auto-refreshing is performed at an appropriate interval. After the recovery, wait for the time

required by the SDRAM before accessing the SDRAM (the time depends on the DDR-

SDRAM; for example, the requirements might be for 130 ns before issuing a command other

than a read command, and 200 clock cycles before issuing a read command).

command so that all memory rows are refreshed.

delay adjustment unit in the DDRIF operate.

refreshing at a regular interval. After this, normal memory access is possible.

Power-Down Mode (when CKE Goes Low)

Related parts for R8A77800ANBGAV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: