Z0847006PSG Zilog, Z0847006PSG Datasheet - Page 159

Z0847006PSG

Manufacturer Part Number

Z0847006PSG

Description

IC 6MHZ Z80 NMOS DART 40-DIP

Manufacturer

Zilog

Series

Z80r

Datasheet

1.Z0847006PSG.pdf

(330 pages)

Specifications of Z0847006PSG

Processor Type

Z80

Features

Dual Channel Asynchronous Receiver/Transmitter (DART)

Speed

6MHz

Voltage

5V

Mounting Type

Through Hole

Package / Case

40-DIP (0.620", 15.75mm)

Mounting Style

Through Hole

Cpu Speed

6MHz

Digital Ic Case Style

DIP

No. Of Pins

40

Supply Voltage Range

5V

Operating Temperature Range

0°C To +70°C

Svhc

No SVHC (18-Jun-2010)

Base Number

847006

Rohs Compliant

Yes

Clock Frequency

6MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

Z0847006PSG

Manufacturer:

Zilog

Quantity:

22

- Current page: 159 of 330

- Download datasheet (3Mb)

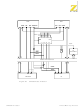

UM008101-0601

Table 18. Transmit Event Sequence (Continued)

In an interrupt-driven CPU transfer scheme, the SIO must interrupt the CPU

whenever it has received a character or needs another character to transmit.

A very short benchmark service routine, which assumes the exclusive use of

the Z80 CPU’s alternate register set for SIO interrupt handling, is provided

below.The numbers in parentheses are clock periods per instruction.

Before the service routine can be executed, the CPU must have its inter-

rupts enabled, finish its current instruction, and execute an interrupt

acknowledge cycle (19 clock periods). This optimistic benchmark takes at

least 68 clock periods per byte transferred, and severely restricts CPU

activity by permanently occupying the alternate register set.

To compare these transfer methods, the ratios of clock cycles used per

Kbaud to clock cycles available per second can be calculated. These

Event

DMA I/O write cycle begins

DMA terminates BUSREQ

DMA I/O write cycle ends

CPU terminates BUSACK and

regains control of bus

SIOSVC:

EXX

OUTI

JRZ,BLKEND

EXX

EI

RETI

; get transfer parameters

; transfer a byte,

; update parameters

; test for end-of-block

; save parameters

; reenable interrupts

Inter-event delay

(clock periods)

1

1

1

3

(4)

(16)

(7)

(4)

(4)

(14)

< % 2 7 2 G T K R J G T C N U

Direct Memory Access

latency, bus occupancy

latency, bus occupancy

bus occupancy

latency, bus occupancy

7 U G T / C P W C N

Related parts for Z0847006PSG

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Customer Procurement Spec(CPS)

Manufacturer:

ZILOG [Zilog, Inc.]

Datasheet:

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet: