Z0847006PSG Zilog, Z0847006PSG Datasheet - Page 170

Z0847006PSG

Manufacturer Part Number

Z0847006PSG

Description

IC 6MHZ Z80 NMOS DART 40-DIP

Manufacturer

Zilog

Series

Z80r

Datasheet

1.Z0847006PSG.pdf

(330 pages)

Specifications of Z0847006PSG

Processor Type

Z80

Features

Dual Channel Asynchronous Receiver/Transmitter (DART)

Speed

6MHz

Voltage

5V

Mounting Type

Through Hole

Package / Case

40-DIP (0.620", 15.75mm)

Mounting Style

Through Hole

Cpu Speed

6MHz

Digital Ic Case Style

DIP

No. Of Pins

40

Supply Voltage Range

5V

Operating Temperature Range

0°C To +70°C

Svhc

No SVHC (18-Jun-2010)

Base Number

847006

Rohs Compliant

Yes

Clock Frequency

6MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

Z0847006PSG

Manufacturer:

Zilog

Quantity:

22

- Current page: 170 of 330

- Download datasheet (3Mb)

UM008101-0601

< % 2 7 2 G T K R J G T C N U

7 U G T / C P W C N

Figure 59.

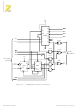

To write to the DMA control bites, the following conditions must be met:

•

•

•

Reading Status Bytes

Figure 60 illustrates the timing needed for the CPU to read the DMA’s read

registers, RR6 through RR0, while the CPU is bus master. To read a regis-

ter, this condition must be met: The CE, IORQ, and RD lines must be

active and stabilized over two rising edges of the clock.

Status data becomes available on the data bus at the time of the second

clock rising edge, which remains on the bus for as long as both the CE,

IORQ, and RD lines remain active.

The DMA’s CE line must be Low (normally done by decoding the

lower byte of the address bus).

The IORQ and WR lines must be Low at this time.

The control byte must be placed on the data bus so that it is stabilized

at a rising clock edge, which occurs one clock period after the CE,

IORQ, and WR lines have stabilized.

D7–D0

IORQ

CLK

WR

CE

CPU-to-DMA Write Cycle Requirements

Direct Memory Access

Related parts for Z0847006PSG

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Customer Procurement Spec(CPS)

Manufacturer:

ZILOG [Zilog, Inc.]

Datasheet:

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet: