Z0847006PSG Zilog, Z0847006PSG Datasheet - Page 164

Z0847006PSG

Manufacturer Part Number

Z0847006PSG

Description

IC 6MHZ Z80 NMOS DART 40-DIP

Manufacturer

Zilog

Series

Z80r

Datasheet

1.Z0847006PSG.pdf

(330 pages)

Specifications of Z0847006PSG

Processor Type

Z80

Features

Dual Channel Asynchronous Receiver/Transmitter (DART)

Speed

6MHz

Voltage

5V

Mounting Type

Through Hole

Package / Case

40-DIP (0.620", 15.75mm)

Mounting Style

Through Hole

Cpu Speed

6MHz

Digital Ic Case Style

DIP

No. Of Pins

40

Supply Voltage Range

5V

Operating Temperature Range

0°C To +70°C

Svhc

No SVHC (18-Jun-2010)

Base Number

847006

Rohs Compliant

Yes

Clock Frequency

6MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

Z0847006PSG

Manufacturer:

Zilog

Quantity:

22

- Current page: 164 of 330

- Download datasheet (3Mb)

UM008101-0601

< % 2 7 2 G T K R J G T C N U

7 U G T / C P W C N

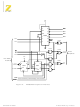

Figure 56.

Many processors encode their control signals, as does the Z80’s M1,

MREQ, IORQ, RD, and WR, into status words that are often demultiplexed

before they are distributed to memory, peripherals, and more. Link the

DMA to these demultiplexed signals and take advantage of tristate

decoders to float the outputs when the DMA is master.

The DMA’s Z80-like control signals must usually be retimed to meet the

requirements of the foreign buses. But the programmable timing feature of

the DMA may well reduce the hardware costs incurred.

Interrupt Request, Acknowledge, and Return

When using the DMA with other processors, this area is the most chal-

lenging because of the many methods of signaling, prioritizing, identifying,

responding to, and returning from interrupts.

Multiplexed

Data Bus

Address

and

CPU

Connecting DMA to Demultiplexed Address/Data Buses

Buffered Bidirectional Data Bus

3-Stage

Latches

Latched Address Bus

DMA

Direct Memory Access

Related parts for Z0847006PSG

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Customer Procurement Spec(CPS)

Manufacturer:

ZILOG [Zilog, Inc.]

Datasheet:

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet: