Z0847006PSG Zilog, Z0847006PSG Datasheet - Page 162

Z0847006PSG

Manufacturer Part Number

Z0847006PSG

Description

IC 6MHZ Z80 NMOS DART 40-DIP

Manufacturer

Zilog

Series

Z80r

Datasheet

1.Z0847006PSG.pdf

(330 pages)

Specifications of Z0847006PSG

Processor Type

Z80

Features

Dual Channel Asynchronous Receiver/Transmitter (DART)

Speed

6MHz

Voltage

5V

Mounting Type

Through Hole

Package / Case

40-DIP (0.620", 15.75mm)

Mounting Style

Through Hole

Cpu Speed

6MHz

Digital Ic Case Style

DIP

No. Of Pins

40

Supply Voltage Range

5V

Operating Temperature Range

0°C To +70°C

Svhc

No SVHC (18-Jun-2010)

Base Number

847006

Rohs Compliant

Yes

Clock Frequency

6MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

Z0847006PSG

Manufacturer:

Zilog

Quantity:

22

- Current page: 162 of 330

- Download datasheet (3Mb)

UM008101-0601

< % 2 7 2 G T K R J G T C N U

7 U G T / C P W C N

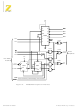

the Z80 bus, to function. These functions are described in the following

sections, and design solutions are offered:

•

•

•

Bus Request/Release Mechanisms

The most fundamental characteristic that distinguishes the Z80 DMA from

other monolithic DMACs is its full control of the system bus during its

active state. Therefore, processors using the DMA must be able to give up

control of the system bus, including address, data, and the control lines

MREQ, IORQ, RD, and WR (or their equivalents). Some processors have

no mechanism for freeing the bus. Others, including the 6800, have rudi-

mentary bus control facilities, but because of their internal dynamic logic

implementations, cannot relinquish control for indefinite periods of time.

This makes them difficult to interface to the DMA.

Many popular microprocessor CPUs, however, do have adequate bus

control facilities, and some are very similar to the Z80 BUSREQ and

BUSACK signals. For instance, the 8080, 8085, and 8086 signals HOLD

and HLDA are very close approximations.

The active levels of HOLD and HLDA are positive rather than negative,

and variations exist in timing. But the use of HOLD and HLDA allows the

address and data bus drivers to be put into their high-impedance states. In

8080 systems using an 8238 to demultiplex commands, the MEMW,

MEMR, IOW, and IOR control lines can be floated using the BUSEN

input. With the 8085, a tristate decoder allows decode or disable corre-

sponding signals. The 8086 and its support chips also tristate their control

signals when HLDA is active.

Bus request/release mechanisms

Bus characteristics

Interrupt request, acknowledge, and return

Direct Memory Access

Related parts for Z0847006PSG

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Customer Procurement Spec(CPS)

Manufacturer:

ZILOG [Zilog, Inc.]

Datasheet:

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet: