UPD70F3740GC-UEU-AX Renesas Electronics America, UPD70F3740GC-UEU-AX Datasheet - Page 481

UPD70F3740GC-UEU-AX

Manufacturer Part Number

UPD70F3740GC-UEU-AX

Description

MCU 32BIT V850ES/JX3 100-LQFP

Manufacturer

Renesas Electronics America

Series

V850ES/Jx3r

Datasheet

1.UPD70F3739GC-UEU-AX.pdf

(889 pages)

Specifications of UPD70F3740GC-UEU-AX

Core Processor

RISC

Core Size

32-Bit

Speed

32MHz

Connectivity

CSI, EBI/EMI, I²C, UART/USART

Peripherals

DMA, LVD, PWM, WDT

Number Of I /o

84

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

40K x 8

Voltage - Supply (vcc/vdd)

2.85 V ~ 3.6 V

Data Converters

A/D 12x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPD70F3740GC-UEU-AX

Manufacturer:

NEC

Quantity:

300

Company:

Part Number:

UPD70F3740GC-UEU-AX

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

UPD70F3740GC-UEU-AX

Manufacturer:

RENESAS/瑞萨

Quantity:

20 000

- Current page: 481 of 889

- Download datasheet (11Mb)

V850ES/JG3

15.6.4 SBF reception

UAnCTL0.UAnRXE bit to 1.

detection is performed.

interrupt request signal (INTUAnR) is output. The UAnOPT0.UAnSRF bit is automatically cleared and SBF reception ends.

Error detection for the UAnSTR.UAnOVE, UAnSTR.UAnPE, and UAnSTR.UAnFE bits is suppressed and UART

communication error detection processing is not performed. Moreover, data transfer of the UARTAn reception shift register

and UAnRX register is not performed and FFH, the initial value, is held. If the SBF width is 10 or fewer bits, reception is

terminated as error processing without outputting an interrupt, and the SBF reception mode is returned to. The UAnSRF

bit is not cleared at this time.

R01UH0015EJ0300 Rev.3.00

Sep 30, 2010

The reception enabled status is achieved by setting the UAnCTL0.UAnPWR bit to 1 and then setting the

The SBF reception wait status is set by setting the SBF reception trigger (UAnOPT0.UAnSTR bit) to 1.

In the SBF reception wait status, similarly to the UART reception wait status, the RXDAn pin is monitored and start bit

Following detection of the start bit, reception is started and the internal counter counts up according to the set baud rate.

When a stop bit is received, if the SBF width is 11 or more bits, normal processing is judged and a reception complete

Cautions 1. If SBF is transmitted during a data reception, a framing error occurs.

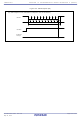

(a) Normal SBF reception (detection of stop bit in more than 10.5 bits)

2. Do not set the SBF reception trigger bit (UAnSRT) and SBF transmission trigger bit (UAnSTT) to 1

during an SBF reception (UAnSRF = 1).

INTUAnR

interrupt

RXDAn

UAnSRF

1

CHAPTER 15 ASYNCHRONOUS SERIAL INTERFACE A (UARTA)

Figure 15-9. SBF Reception (1/2)

2

3

4

5

6

11.5

7

8

9

10

11

Page 465 of 870

Related parts for UPD70F3740GC-UEU-AX

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: