UPD70F3740GC-UEU-AX Renesas Electronics America, UPD70F3740GC-UEU-AX Datasheet - Page 794

UPD70F3740GC-UEU-AX

Manufacturer Part Number

UPD70F3740GC-UEU-AX

Description

MCU 32BIT V850ES/JX3 100-LQFP

Manufacturer

Renesas Electronics America

Series

V850ES/Jx3r

Datasheet

1.UPD70F3739GC-UEU-AX.pdf

(889 pages)

Specifications of UPD70F3740GC-UEU-AX

Core Processor

RISC

Core Size

32-Bit

Speed

32MHz

Connectivity

CSI, EBI/EMI, I²C, UART/USART

Peripherals

DMA, LVD, PWM, WDT

Number Of I /o

84

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

40K x 8

Voltage - Supply (vcc/vdd)

2.85 V ~ 3.6 V

Data Converters

A/D 12x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPD70F3740GC-UEU-AX

Manufacturer:

NEC

Quantity:

300

Company:

Part Number:

UPD70F3740GC-UEU-AX

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

UPD70F3740GC-UEU-AX

Manufacturer:

RENESAS/瑞萨

Quantity:

20 000

- Current page: 794 of 889

- Download datasheet (11Mb)

V850ES/JG3

Bus Timing

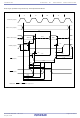

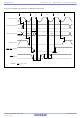

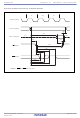

(1) In multiplexed bus mode

(a) Read/write cycle (CLKOUT asynchronous)

(T

Remarks 1. t

R01UH0015EJ0300 Rev.3.00

Sep 30, 2010

A

Address setup time (to ASTB↓)

Address hold time (from ASTB↓)

Delay time from RD↓ to address float

Data input setup time from address

Data input setup time from RD↓

Delay time from ASTB↓ to RD, WRm↓

Data input hold time (from RD↑)

Address output time from RD↑

Delay time from RD, WRm↑ to ASTB↑

Delay time from RD↑ to ASTB↓

RD, WRm low-level width

ASTB high-level width

Data output time from WRm↓

Data output setup time (to WRm↑)

Data output hold time (from WRm↑)

WAIT setup time (to address)

WAIT hold time (from address)

WAIT setup time (to ASTB↓)

WAIT hold time (from ASTB↓)

= −40 to +85°C, V

Caution When operating at f

2. T = 1/f

3. n: Number of wait clocks inserted in the bus cycle

4. m = 0, 1

5. i: Number of idle states inserted after a read cycle (0 or 1)

6. The values in the above specifications are values for when clocks with a 1:1 duty ratio are input from X1.

t

The sampling timing changes when a programmable wait is inserted.

ASW

AHW

Parameter

: Number of address setup wait clocks

: Number of address hold wait clocks

CPU

DD

(f

= EV

CPU

: CPU operating clock frequency)

DD

= AV

XX

REF0

> 20 MHz, be sure to insert address hold waits and address setup waits.

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

SAST

HSTA

FRDA

SAID

SRID

DSTRDWR

HRDID

DRDA

DRDWRST

DRDST

WRDWRL

WSTH

DWROD

SODWR

HWROD

SAWT1

SAWT2

HAWT1

HAWT2

SSTWT1

SSTWT2

HSTWT1

HSTWT2

= AV

Symbol

REF1

, V

SS

<10>

<11>

<12>

<13>

<14>

<15>

<16>

<17>

<18>

<19>

<20>

<21>

<22>

<23>

<24>

<25>

<26>

<27>

<28>

<6>

<7>

<8>

<9>

= EV

CHAPTER 29

n ≥ 1

n ≥ 1

n ≥ 1

n ≥ 1

SS

Conditions

= AV

SS

= 0 V, C

(1.5

(1 + i + t

(0.5

(1.5

(0.5 + t

(0.5 + t

(0.5 + t

(1

(1

(1

(1

+

+

+

(n + t

0.5T − 15

+

L

n + t

n + t

i + t

+

+

+

T − 15

n + t

ELECTRICAL SPECIFICATIONS

= 50 pF)

MIN.

n)T − 15

n)T − 20

ASW

AHW

AHW

i)T − 15

ASW

0

ASW

ASW

ASW

AHW

)T − 20

)T − 15

)T − 15

AHW

)T − 15

+ t

+ t

)T − 15

)T

AHW

AHW

)T

)T

)T

(2

(1.5

(1

(1.5 + t

(1 + t

+

+

n + t

+

(1

n + t

n + t

ASW

+

ASW

MAX.

AHW

ASW

n)T − 25

16

15

+ t

AHW

+ t

+ t

)T − 25

AHW

AHW

AHW

)T − 25

Page 778 of 870

)T − 35

)T − 35

)T − 35

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Related parts for UPD70F3740GC-UEU-AX

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: