TMP92xy26AXBG Toshiba, TMP92xy26AXBG Datasheet - Page 295

TMP92xy26AXBG

Manufacturer Part Number

TMP92xy26AXBG

Description

Manufacturer

Toshiba

Datasheet

1.TMP92XY26AXBG.pdf

(768 pages)

Specifications of TMP92xy26AXBG

Package

FPGA228

Rom Types(m=mask,p=otp, F=flash,e=eeprom)

Romless

Rom Combinations

Romless

Ram Combinations

144/288

Architecture

32-bit CISC

Usb/spi Channels

1/1

Uart/sio Channels

2

I2c/sio Bus Channels

1

(s)dram Controller

1

Adc 10-bit Channel

6

Da Converter

-

Timer 8-bit Channel

8

Timer 16-bit Channel

2

Pwm 8-bit Channels

-

Pwm 16-bit Channels

-

Cs/wait Controller

4

Dual Clock

Y

Number Of I/o Ports

136

Power Supply Voltage(v)

3.0 to 3.6

- Current page: 295 of 768

- Download datasheet (6Mb)

TA0REG-WR

(INTTA0 interrupt)

(4) 8-bit PWM (Pulse width modulation) output mode

TA0IN

TA0REG and

φT16

φT1

φT4

UC0 match

resolution of 8 bits can be output.

PM1). TMRA1 can also be used as an 8-bit timer.

timer register TA0REG or when 2

TA01MOD<PWM01:00>). The up counter UC0 is cleared when 2

occurs.

TA01MOD<TA0CLK1:0>

TA1OUT

overflow

This mode is only valid for TMRA0. In this mode, a PWM pulse with the maximum

When TMRA0 is used the PWM pulse is output on the TA1OUT pin (Shared with

The timer output is inverted when the up counter (UC0) matches the value set in the

The following conditions must be satisfied before this PWM mode can be used.

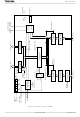

Figure 3.12.24 shows a block diagram representing this mode.

TA01RUN<TA0RDE>

2

Value set in TA0REG < Value set for 2n counter overflow

Value set in TA0REG ≠ 0

Selector

n

Selector

Figure 3.12.24 Block Diagram of 8-Bit PWM Mode

Figure 3.12.23 8-Bit PWM Waveforms

Shift trigger

Internal data bus

8-bit up counter

Register buffer

Comparator

TA0REG

(UC0)

92CF26A-293

n

counter overflow occurs (n = 6, 7 or 8 as specified by

Clear

2

TA01RUN<TA0RUN>

n

control

overflow

Overflow

(PWM cycle)

t

PWM

TA01MOD

<PWM01:00>

TA1OUT

TA1FF

n

counter overflow

TMP92CF26A

Inversion

2009-06-25

INTTA0

TA1FFCR

<TA1FFIE>

Related parts for TMP92xy26AXBG

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: